利用FPGA實現(xiàn)小型聲納的片上系統(tǒng)集成與信息技術(shù)服務(wù)

隨著信息技術(shù)的飛速發(fā)展,小型聲納系統(tǒng)在海洋探測、水下通信和安防監(jiān)控等領(lǐng)域的應(yīng)用日益廣泛。基于FPGA(現(xiàn)場可編程門陣列)的片上系統(tǒng)(SoC)集成技術(shù),為小型聲納設(shè)備的優(yōu)化提供了強大的解決方案。本文將探討如何利用FPGA實現(xiàn)小型聲納的片上系統(tǒng)集成,并分析其在信息技術(shù)服務(wù)中的價值與應(yīng)用前景。

FPGA在小型聲納系統(tǒng)中的優(yōu)勢

FPGA以其高度可編程性、并行處理能力和低功耗特性,成為小型聲納系統(tǒng)的理想選擇。在聲納系統(tǒng)中,信號處理是關(guān)鍵環(huán)節(jié),包括回聲信號的采集、濾波、特征提取和目標識別等。FPGA能夠通過硬件描述語言(如Verilog或VHDL)定制數(shù)字信號處理(DSP)模塊,實現(xiàn)高速并行計算,顯著提升聲納的實時性能。例如,聲納的回波信號通常需要快速傅里葉變換(FFT)處理,F(xiàn)PGA可以設(shè)計專用硬件加速器,相比傳統(tǒng)CPU或DSP處理器,處理速度提高數(shù)倍,同時降低系統(tǒng)延遲。

小型聲納片上系統(tǒng)集成的實現(xiàn)方法

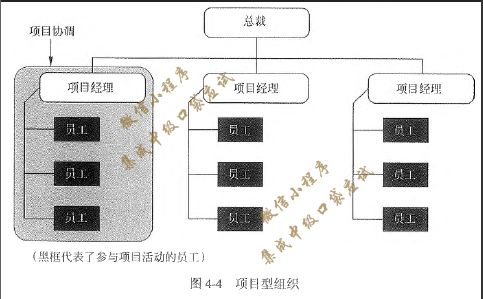

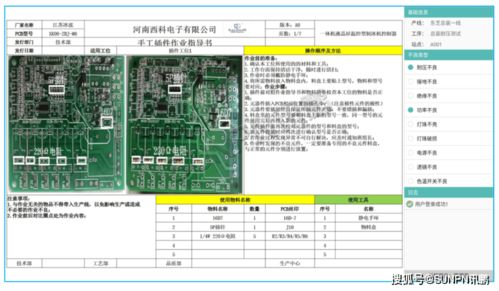

在實現(xiàn)小型聲納的片上系統(tǒng)集成時,首先需要設(shè)計一個基于FPGA的SoC架構(gòu)。該架構(gòu)通常包括軟核處理器(如Xilinx的MicroBlaze或Intel的Nios II)、自定義數(shù)字信號處理模塊、存儲接口和外設(shè)控制單元。通過FPGA的靈活配置,可以將聲納的模擬前端(如傳感器接口和ADC模塊)與數(shù)字處理部分無縫集成,形成一個緊湊的片上系統(tǒng)。例如,利用FPGA的IP核庫,我們可以集成高速ADC控制器,實時采集水下聲波信號;同時,設(shè)計專用的波束成形算法模塊,提高聲納的方向分辨率和抗干擾能力。這種集成不僅減少了系統(tǒng)的物理尺寸和功耗,還通過硬件優(yōu)化提升了整體可靠性。

信息技術(shù)服務(wù)在聲納系統(tǒng)集成中的應(yīng)用

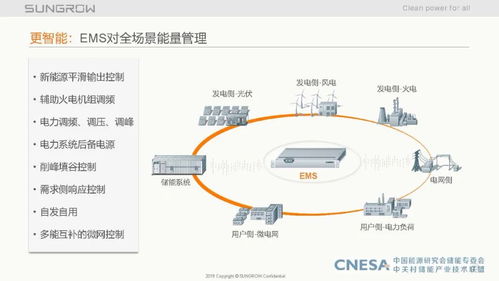

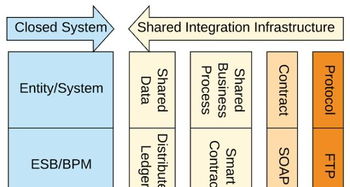

信息技術(shù)服務(wù)在小型聲納的FPGA集成中扮演著至關(guān)重要的角色。從系統(tǒng)設(shè)計階段,IT服務(wù)可以提供EDA(電子設(shè)計自動化)工具支持,如使用Vivado或Quartus進行FPGA開發(fā)和仿真,確保設(shè)計符合性能指標。在部署階段,云平臺和物聯(lián)網(wǎng)技術(shù)可以用于遠程監(jiān)控和維護聲納系統(tǒng),例如通過無線通信模塊將聲納數(shù)據(jù)傳輸至云端,結(jié)合大數(shù)據(jù)分析實現(xiàn)智能目標識別和預(yù)測性維護。信息技術(shù)服務(wù)還能提供安全解決方案,保護聲納系統(tǒng)免受網(wǎng)絡(luò)攻擊,確保水下探測數(shù)據(jù)的機密性和完整性。

應(yīng)用前景與挑戰(zhàn)

基于FPGA的小型聲納片上系統(tǒng)集成,在海洋資源勘探、水下機器人導航和軍事偵察等領(lǐng)域具有廣闊的應(yīng)用前景。隨著人工智能技術(shù)的發(fā)展,未來可以將深度學習模型部署到FPGA中,實現(xiàn)更智能的聲納目標分類。這一技術(shù)也面臨挑戰(zhàn),如FPGA設(shè)計復(fù)雜度高、開發(fā)周期長,以及系統(tǒng)功耗和散熱問題。通過結(jié)合先進的IT服務(wù),例如自動化設(shè)計工具和云邊協(xié)同計算,可以有效克服這些挑戰(zhàn),推動小型聲納系統(tǒng)向更高效、智能的方向發(fā)展。

利用FPGA實現(xiàn)小型聲納的片上系統(tǒng)集成,不僅提升了系統(tǒng)的性能和集成度,還通過信息技術(shù)服務(wù)增強了其可擴展性和智能化水平。隨著技術(shù)的不斷進步,這種集成方案將在水下探測領(lǐng)域發(fā)揮越來越重要的作用。

如若轉(zhuǎn)載,請注明出處:http://www.hlsty.cn/product/12.html

更新時間:2026-03-01 15:40:59